◆JEVeC DAY 2020 Online 開催概要

名 称 : JEVeC DAY 2020 Online

会 期 : 2020年12月14日(月) 10:00-17:00

~2020年12月31日(木)まで講演動画視聴、資料ダウンロードできます

会 場 : Zoomによるオンライン開催

専用URLを登録者にメールでお知らせいたします

参加費 : 無料(事前登録制)

申 込 : こちら(https://jevec.jp/jevecday2020online/)よりお申し込みください。

技術展示の公開スライドはこちら

今年の JEVeC DAY 2020 Online は、場所はオンラインに変わりますが、EDA の最新技術に触れられる和気あいあいお祭り縁日のようなイベントになることは、例年と全く変わりません。今年も、電子機器・半導体の設計技術に関わる方々を対象に、最新かつ質の高い情報をご提供する講演会・チュートリアル・技術紹介と、JEVeC 会員企業や招待企業の技術をずらりと並べた展示コーナーをお楽しみください。また、久しぶりの方に予期せず出会えるネットならではの参加者同士の交流コーナーも準備しています。ぜひお楽しみにご参加ください。JEVeC は JEVeC DAY 2020 Online を通じて今後の業界の発展と楽しさの増進に寄与してまいります。

◆展示概要

(株)インターバディは、電子機器開発向けソリューションを提供しています。

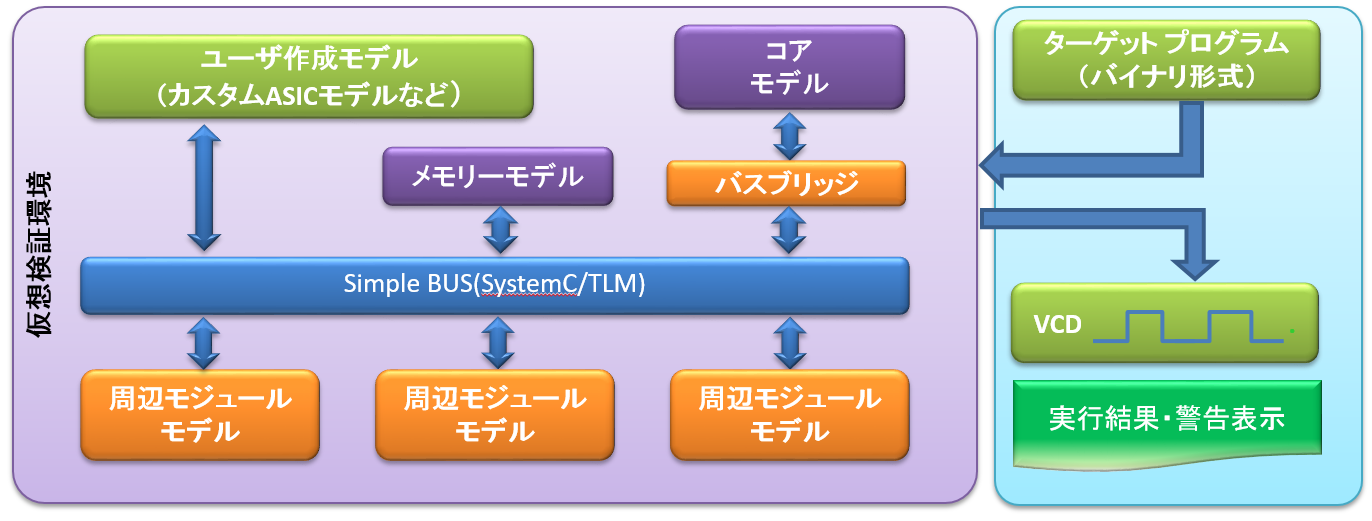

「電子機器向け組込ソフト開発の技、あれこれ」と題して、仮想検証向けSystemCモデル(SyDAPmodel)等をご紹介します。

◆SyDAP model

SyDAP model (サイダップモデル) System Debug Assist Peripheral model

システムデバッグを支援する仮想検証向けのマイコン周辺モジュールのSystemCモデル群です。

SystemC/TLM2.0に準拠した標準的なインターフェイスなので既存の仮想検証環境にも容易に組み込むことができ、かつ機能部はC言語で実装することで高速に動作させることができます。

ARM(R) Cortex(R) M4 (*)コアのマイコン検証にも対応するため、FastModels とのI/Fにも対応しています。 CPUコアとはブリッジを介してTLM仕様でI/Fをしておりますので、高い相互運用性があります。

(* ARM Cortex は ARM Ltd. の登録商標です)

◆仮想検証用マイコン周辺モジュール

◆標準仕様 SystemC / TLM2.0 準拠

◆実行速度重視 LT (Loosely Timed)

◆ターゲットプログラムのデバックに専念

◆ユーザ作成モデルも組み込み検証可能

◆警告表示機能でレジスタ設定ミスも容易に発見

◆容易な故障注入でISO26262対策にも利用可能

組込システム開発、検証業務も得意としておりますので、お気軽にお問い合わせ下さい。

担当者と直接話せる 展示Q&Aコーナー を用意しております。

12/14(月)16:20~17:00 Zoomミーティングにてお待ちしております。

当日公開される登録者専用ページの インターバディ のヘッドセットアイコンをクリックしてご参加下さい。

InterBuddy

InterBuddy