展示会概要、参加登録はこちらへ

EdgeTech+2022 のサイトへ

◆株式会社インターバディはEdgeTech+2022オンラインに出展します。

昨年11月16日(水)から3日間、パシフィコ横浜にて開催されました「EdgeTech+ 2022」のオンライン開催が1月10日(火)- 2月10日(金)に行われます。

名 称 : EdageTech+2022

会 期 : 2023年1月10日(火)- 2月10日(金)

会 場 : オンライン

ブース : 入場登録の上こちらをクリック

電子設計・EDAトラック(パワースピンを除く)は次の日程で視聴できます。

1月23日(月)10:00 ~ 1月30日(月)9:59

2月6日(月)10:00 ~ 2月10日(金)17:00

◆株式会社インターバディはEdgeTech+2022に出展します。

弊社のコア技術はソフトウェア開発です。特にEDA(Electronic Design Automation:半導体自動設計)、組込システムを得意としております。 組込ソフトウェア開発向けの仮想検証用マイコン周辺モジュールのSystemCモデル群を製品としてご提供も行っております。

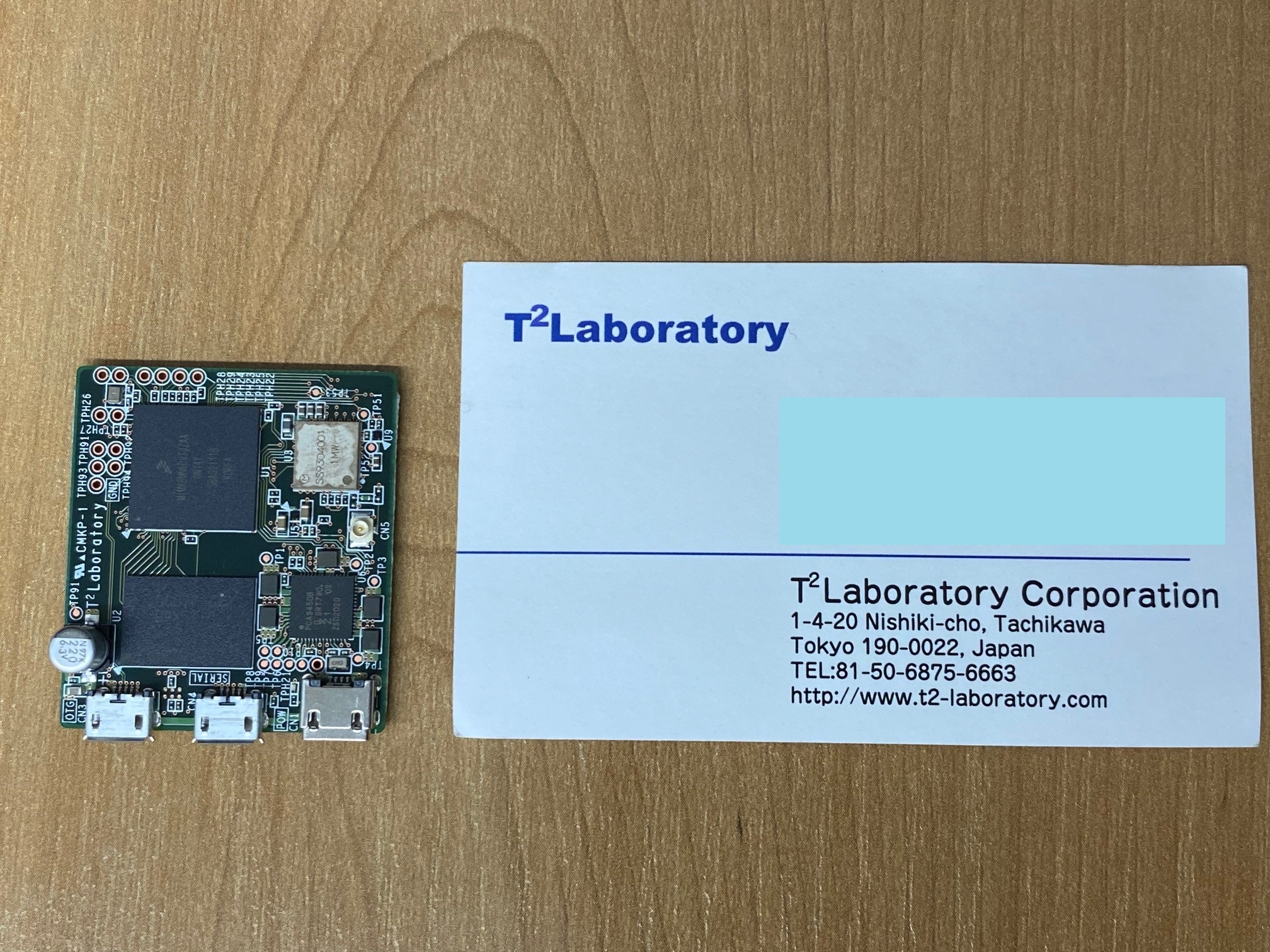

電子システム開発に関してもパートナー(株式会社ティーツー・ラボラトリ)と共にお手伝いします。

◆開催概要

名 称 : EdageTech+2022

会 期 : 2022年11月16日(水)~18日(金)

10:00~17:00(11月17日(木)は~18:00まで)

会 場 : パシフィコ横浜

ブース : B-W05(電子設計・EDAパビリオン)

◆EdgeTech+フェスタ

日 時 : 2022年11月17日(木) 17:00-18:00

会 場 : 展示会場内

3年ぶりに『フェスタ』が復活!電子設計・EDAパビリオンでもお飲み物と軽食をご用意して皆様のお越しをお待ちしております。

フランクな情報交換や久しぶりの同窓会もお楽しみください。

◆展示概要

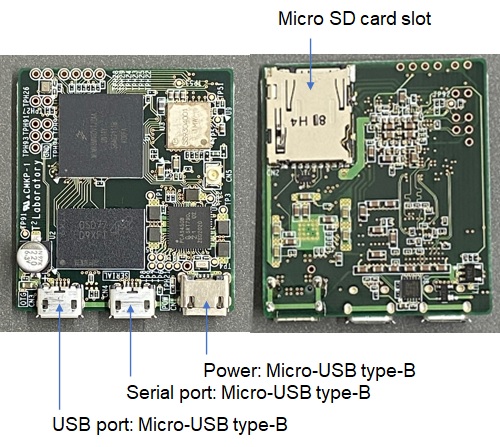

◆◆T2Laboratory社製IoT向けAIエッジコンピュータを初披露

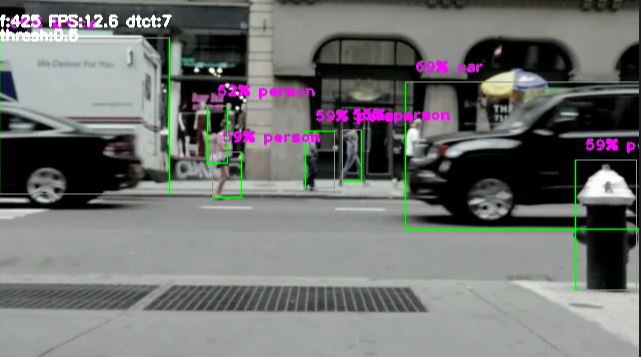

IoT製品ではAIなどエッジ機能の高度化で処理能力は増加する一方、省電力小型 化が必須です。IoT向けAIエッジコンピュータの開発プラットフォームでは、AI で標準的なUbuntuを搭載し、約1Wで12FPSの物体認識性能を達成。更に名刺サイ ズ1/2以下の世界最小クラスの超小型化を実現しました。

PC、RaspberryPi、AIエッジコンピュータにてディープラーニングのデモアプリを動作させますので、それぞれの環境の違い、特性などを体感できます。

・顔認識/顔識別

・物体検出、等々

これらの技術をベースにお客様 のIoT製品に沿った電子設計サービス(仕様設計、部品選定、回路・レイアウト 設計、試作、ファームウエア開発)もご提供致します。

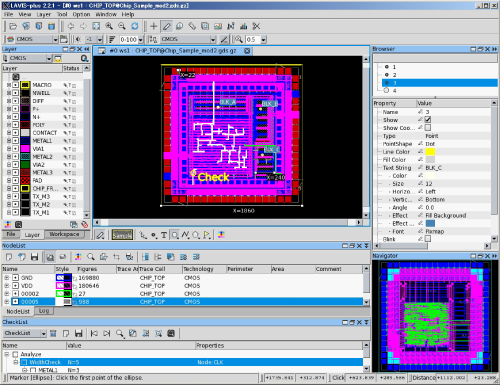

◆◆TOOL社製LAVIS-plus

大規模データを超高速に読み込み表示するビューア機能に加え、電気特性解析や検証エラー表示、簡易エディタとしても活用いただける「ICデザイン視覚検証ツール」です。

視覚検証ツール「LAVIS」の後継としてリリースされ、LAVIS の最大の特長である大規模設計データの超高速表示や省メモリ、他社製ツールとの親和性の高さを継承しながら、パフォーマンスや操作性、拡張性など、あらゆる面で LAVIS を超えるスペックとなっています。

LSI 設計データの大規模かつ微細化にともない、市場投入までの期間、いわゆる time to market の短縮と、早期段階から歩留まりを考慮した設計が重要となる中で、LAVIS-plus はこうした課題を設計から検証、マスク製造、検査、不良解析にいたるさまざまな工程で解決することができます。

詳しくは、https://www.tool.co.jp/products/lavis-plus/ を参照下さい。

◆◆SyDAP model

電子機器開発では、実現手段をハード/ソフトに分割後、設計まではハード・ソフトを並行して行えますが、 ソフト実装、特に検証(デバッグ)はハードが出来上がった後に行うこととなり、 ハード実装が遅れるとソフト検証の開始も遅れることになります。

しかし製品リリース時期は簡単に変更はできないため、結果としてソフト検証に充てられる期間は短くなってしまいます。 これを解消するためにハード実装を待たずにソフト検証を開始できる仮想環境での検証が求められています。

インターバディでは、仮想検証向け周辺モジュール(SystemC/TLM2.0準拠)モデルを整備し、 既に実ユーザに導入され仮想検証でご利用頂いております。

ARM(R) Cortex(R) M4 コアのマイコン検証にも対応するため、 FastModels とのI/Fにも対応しました。 CPUコアとはブリッジを介してTLM仕様でI/Fをしておりますので、高い相互運用性があります。

SyDAP model (サイダップモデル) System Debug Assist Peripheral model

システムデバッグを支援する仮想検証向けのマイコン周辺モジュールのSystemCモデル群です。

SystemC/TLM2.0に準拠した標準的なインターフェイスなので既存の仮想検証環境にも容易に組み込むことができ、かつ機能部はC言語で実装することで高速に動作させることができます。

- 機能モジュール毎に独立、 I/F部コードは公開

- ユーザ作成モデルも容易に組み込み

- 警告表示機能でレジスタ設定ミスも容易に発見

- 柔軟な故障注入でISO26262対策にも

◆講演

日 時 : 2022年11月17日(木) 13:30-16:15

会 場 : 展示会場内 セミナー会場A A2-04

URL : 説明ページ、事前登録はこちら

概 要 : 電子設計・EDAトラック

システム開発における電子設計や半導体設計にフォーカスした専門トラックです。

次世代を担う注目の最先端技術開発の最新情報と現場で直面する課題と対策を紹介します。半導体設計者は勿論、電子機器開発者や組込ソフトウェア開発者にも必見の内容が盛り沢山です。

・大容量&高速メモリの設計手法

フラットーク株式会社

・[招待講演]AI/IoTに向けた高エネルギー効率な不揮発FPGA

ナノブリッジ・セミコンダクター株式会社・技術責任者・阪本 利司

・IoTプラットフォームへ組込むLSIの開発とその活用

CMエンジニアリング株式会社

・[招待講演]東北大学発スピントロニクス省電力半導体技術で、

カーボンニュートラル時代の半導体ゲームチェンジャ―を目指す!

パワースピン株式会社 代表取締役&CTO 遠藤 哲郎

・ローカルクラウドとオープンソースEDAによるLSI設計環境

株式会社CDC研究所

◆EDAツール開発、組込システム開発も得意としておりますので、お気軽にお声掛け下さい。

InterBuddy

InterBuddy